Over 20 Years of experiment-S – and Still Going Strong

Over 20 years – that’s how long we’ve been working on this project. It is therefore probably the longest-maintained long-term project in the field of digital modeling of Atari-relevant hardware. And quite a lot has happened during that time. If you’re already familiar with this project and website, feel free to keep reading from here. For those visiting for the first time, you’ll find the original text and development history in the current entry of the logbook.

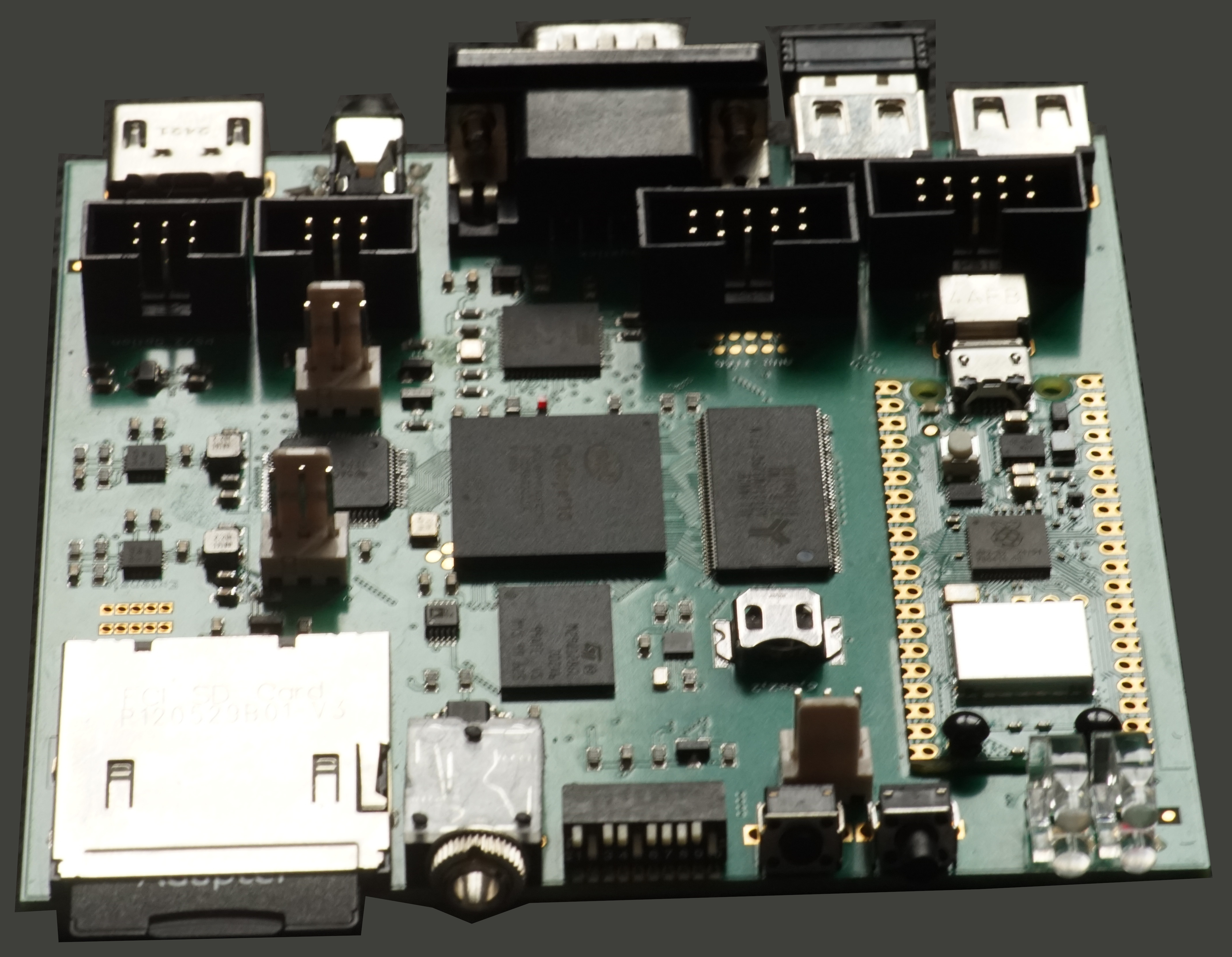

Suska stands for the implementation of various Atari computers in Field Programmable Gate Arrays (FPGAs), as well as for the development of various FPGA-based hardware components. Suska-IV-B is the latest representative – a fourth-generation board. This hardware will be available in our shop starting in end of July. Thanks to the consistent development of the FPGA core and the corresponding hardware, we’ve achieved something truly special:

The Falcon Lives!

The Suska-IV-B hardware is, of course, only as good as its FPGA core – the modeling within the FPGA. And we had something special in mind: it was meant to be a Falcon, and it became a Falcon+. Unlike the original, however, it features 48MB ALTRAM, 14MB RAM, a 32-bit data bus, a USB subsystem, Wi-Fi capability via PicoWIFI, an HDMI video interface, and various expansion options. You can find photos of it in the gallery. Currently, the FPGA core does not yet include the Falcon’s characteristic Digital Signal Processor (DSP). It is in development, but was temporarily put on hold due to work on the USB subsystem and other components.

Suska-IV-B with the Falcon core can run under various operating systems. The current version of EmuTOS has proven to be very stable and user-friendly. However, TOS404 also runs with minor adjustments. For legal reasons, the boards are shipped with EmuTOS.

The Shop

There’s news in our shop as well. All third-generation Suska boards are sold out. Smaller peripheral devices such as the GigaFile and the ACSI-SCSI solutions will be sold off in their current form. We will no longer produce Suska-IV boards for stock, but instead manufacture them to order in a small-scale, handcrafted operation. Suska-IV-B is therefore intended as a very exclusive product.

After more than 20 years, Suska has truly become a long-term project. And working on it is still a joy – let’s keep going…

Enjoy browsing!

Wolfgang