An Open Source Atari ST(E) IP-Core written in VHDL

This is a fun project that has been started because of my interests in modelling digital logic.

Suska has grown to a nearly full functional Atari ST using VHDL as modelling language. At the very beginning it was just the address decoder of the GLUE custom chip which was replaced by a simple model. That was back in February 2003. Many hundreds of hours later all custom chips found in the Atari ST have been replaced with a single FPGA. Even the 68000 CPU has been integrated.

A big challenge after each modelling step was to test the results directly with the Atari main board keeping the same functionality as if they were original chips. For that we used Sphinx modules from Inventronik with a piggy-back and an adapter to replace each custom chip. We have pictures in our gallery if you are interested.

More and more functions of the ST machines have been integrated into a single FPGA. Floppy Disk Controller, Blitter and last but not least the 68000 CPU found its way into the Suska FPGA.

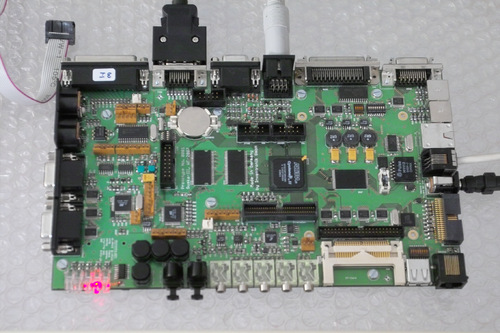

Thanks to a few donations we created the Suska main board. The circuit board includes an Altera (Cyclone II in BGA housing), Flash-Prom, RAM, as well as two Atmel MCs for the boot loader and for programming the FPGAs boot device. The board integrates all the typical Atari ST interfaces. Using other FPGAs from different manufacturers like Actel, Lattice or Xilinx would have been an option too.

The completion of the board lead us to another aspect: The operating system. For debugging purposes and because of copyrights we decided to go with EmuTOS - an open source TOS. Thanks to Jens, debugging became pretty pain free.

Suska is a long term project. The current state can be found in the blog or the progress list.

Have fun with Suska

Wolfgang